TH-C01

The TH-C01 is my first designed and built CPU, just using logic elements. The design has been simulated using the logisim tool.

Definition

- 8 bit ALU

- 8 bit Data bus

- 16 bit Address bus (MAX 64k bytes RAM)

- 8 x 8 bit registers (R0..R7) + (R6+R7 as address pointer)

- Dedicated Stack Pointer

- Dedicated PC

- Interruption control

- Expected 100 Khz

- RISC-like architecture with 3 to 5 cycles per operation

Architecture Details

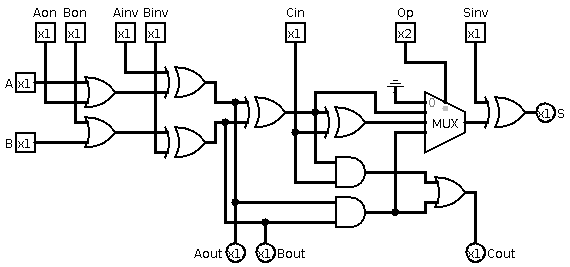

ALU

The ALU can operate two 8 bit data (A and B), and its composed of 8 elements that are basically the same.

INPUTS':

- A: Operand A bit

- B: Operand B bit

- Aon: Enables A bit operand

- Bon: Enables B bit operand

- Ainv: Inverses the A bit operand

- Binv: Inverses the B bit operand

- Cin: Carry in

- Op (2 bits): Chose operation path

- Sinv: Invert the operation result

OUTPUTS':

- S: Operation result

- Aout:

- Bout:

- Cout: Carry out

FLAGS:

- Carry (C):

- Parity (P):

- Adjust (A):

- Zero (Z):

- Negative (N):

- Overflow (O):